集成電路設(shè)計(jì)是現(xiàn)代電子工業(yè)的基石,它將抽象的電路構(gòu)想轉(zhuǎn)化為能在硅片上精確制造的物理實(shí)體。整個(gè)過程可以比作建造一座宏偉的摩天大樓,其中‘集成電路設(shè)計(jì)’是涵蓋從建筑設(shè)計(jì)到結(jié)構(gòu)工程的完整藍(lán)圖規(guī)劃,而‘集成電路布圖設(shè)計(jì)’則是將藍(lán)圖轉(zhuǎn)化為每一塊磚、每一根鋼筋精確位置和連接的施工圖紙。兩者緊密相連,共同構(gòu)成了芯片誕生的核心路徑。

一、集成電路設(shè)計(jì):從構(gòu)想到邏輯

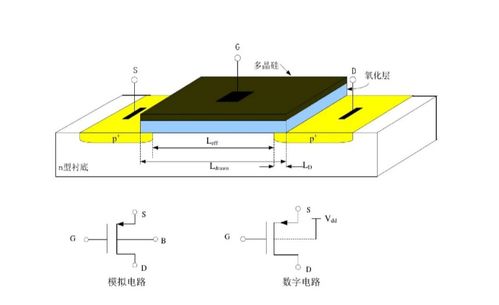

集成電路設(shè)計(jì)是整個(gè)芯片開發(fā)流程的上游環(huán)節(jié),其核心目標(biāo)是將系統(tǒng)功能或算法需求,轉(zhuǎn)化為可供后續(xù)物理實(shí)現(xiàn)的技術(shù)方案。這一過程通常從系統(tǒng)級(jí)設(shè)計(jì)開始,通過硬件描述語言(如Verilog或VHDL)定義芯片的功能和行為,建立‘寄存器傳輸級(jí)’模型。通過邏輯綜合工具,將這一高級(jí)描述轉(zhuǎn)換為由標(biāo)準(zhǔn)邏輯單元(如與門、或門、觸發(fā)器)組成的門級(jí)網(wǎng)表。此時(shí)的電路仍是邏輯和功能層面的抽象描述,確定了‘做什么’,但尚未定義‘如何做’——即晶體管、連線等物理元素在硅片上的具體形態(tài)、位置和連接關(guān)系。

二、集成電路布圖設(shè)計(jì):從邏輯到物理

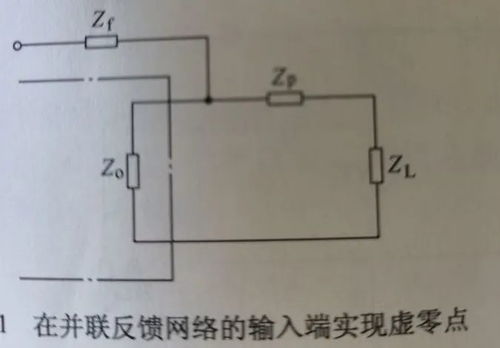

布圖設(shè)計(jì),又稱為物理設(shè)計(jì),是銜接邏輯設(shè)計(jì)與芯片制造的橋梁,是設(shè)計(jì)流程中技術(shù)最密集、挑戰(zhàn)最大的階段之一。其任務(wù)是將門級(jí)網(wǎng)表轉(zhuǎn)化為可供光刻掩模版使用的幾何圖形數(shù)據(jù),即版圖。這個(gè)過程猶如為一座復(fù)雜的城市繪制詳細(xì)的市政地圖,需要精確規(guī)劃每一個(gè)“建筑”(晶體管、邏輯單元)的位置、形狀,以及連接它們的“道路”(互連線)的走向和寬度。

布圖設(shè)計(jì)主要包含以下幾個(gè)關(guān)鍵步驟:

- 布局:確定芯片上各個(gè)功能模塊以及模塊內(nèi)所有標(biāo)準(zhǔn)單元或定制單元的物理位置。布局的目標(biāo)是在滿足時(shí)序、功耗和面積約束的前提下,優(yōu)化單元擺放,為后續(xù)布線創(chuàng)造有利條件,并盡量減少芯片總面積。

- 布線:根據(jù)電路的連接關(guān)系,在已經(jīng)固定的單元之間,按照工藝設(shè)計(jì)規(guī)則,規(guī)劃并生成金屬互連線。布線需要處理數(shù)百萬甚至數(shù)十億個(gè)連接點(diǎn),確保所有信號(hào)正確連通,同時(shí)優(yōu)化線長(zhǎng)以減少延遲和串?dāng)_,并滿足電流承載能力等電學(xué)要求。

- 時(shí)序收斂與優(yōu)化:在布局布線過程中及之后,需要反復(fù)進(jìn)行靜態(tài)時(shí)序分析,確保信號(hào)能在時(shí)鐘約束下正確傳輸。通過調(diào)整單元尺寸、插入緩沖器、優(yōu)化時(shí)鐘樹等方式,解決建立時(shí)間和保持時(shí)間的違規(guī)問題,是布圖設(shè)計(jì)的核心挑戰(zhàn)。

- 物理驗(yàn)證:完成初步版圖后,必須進(jìn)行嚴(yán)格的驗(yàn)證,包括設(shè)計(jì)規(guī)則檢查(確保版圖符合晶圓廠的制造工藝極限)、電氣規(guī)則檢查(檢查電學(xué)連接的合理性)以及版圖與原理圖一致性檢查(確保物理連接與原始邏輯設(shè)計(jì)完全一致)。

三、設(shè)計(jì)與布圖:相輔相成的迭代過程

在實(shí)際項(xiàng)目中,集成電路設(shè)計(jì)與布圖設(shè)計(jì)并非嚴(yán)格的線性流程,而是一個(gè)高度迭代、反復(fù)優(yōu)化的循環(huán)。邏輯設(shè)計(jì)的決策(如架構(gòu)選擇、模塊劃分)會(huì)深刻影響布圖的難度和結(jié)果(如布線擁塞、時(shí)序性能)。反之,布圖階段反饋的物理信息(如實(shí)際線延遲、功耗熱點(diǎn))也可能迫使設(shè)計(jì)階段進(jìn)行修改或優(yōu)化。隨著工藝節(jié)點(diǎn)進(jìn)入納米尺度,這種前后端的協(xié)同設(shè)計(jì)變得至關(guān)重要。先進(jìn)的設(shè)計(jì)方法學(xué),如物理綜合,更是將布局、時(shí)序優(yōu)化等物理信息提前引入邏輯綜合階段,以實(shí)現(xiàn)更好的整體質(zhì)量。

四、面臨的挑戰(zhàn)與未來趨勢(shì)

隨著摩爾定律的持續(xù)推進(jìn),集成電路布圖設(shè)計(jì)面臨著前所未有的挑戰(zhàn):工藝尺寸微縮帶來的量子效應(yīng)、日益嚴(yán)峻的功耗墻、信號(hào)完整性問題、以及設(shè)計(jì)復(fù)雜度的指數(shù)級(jí)增長(zhǎng)。為了應(yīng)對(duì)這些挑戰(zhàn),自動(dòng)化電子設(shè)計(jì)工具的作用愈發(fā)關(guān)鍵,人工智能與機(jī)器學(xué)習(xí)技術(shù)正被廣泛應(yīng)用于布局預(yù)測(cè)、布線優(yōu)化和時(shí)序分析中,以提升設(shè)計(jì)效率和質(zhì)量。基于芯粒的先進(jìn)封裝技術(shù),也使得布圖設(shè)計(jì)從單一的二維平面向2.5D/3D堆疊的立體空間拓展,開辟了新的設(shè)計(jì)維度和優(yōu)化可能。

###

總而言之,集成電路設(shè)計(jì)是賦予芯片‘靈魂’的創(chuàng)意與規(guī)劃過程,而集成電路布圖設(shè)計(jì)則是塑造其‘軀體’的精密與嚴(yán)謹(jǐn)?shù)乃囆g(shù)。二者一脈相承,共同將人類智慧的抽象結(jié)晶,轉(zhuǎn)化為驅(qū)動(dòng)數(shù)字世界的微觀引擎。在信息時(shí)代,掌握并不斷革新這兩項(xiàng)核心技術(shù),是推動(dòng)半導(dǎo)體產(chǎn)業(yè)持續(xù)前進(jìn)的根本動(dòng)力。